Project Info

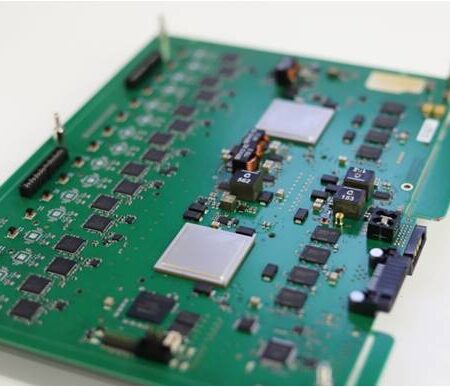

Sanitas EG proposes proprietary video pipeline. It is possible to compose IP Cores to customize your video chain.

Description

| IP_SPort | Sensor Port |

| IP_Stat | Statistics |

| IP_AWB_AGC | Automatic White Balance Automatic Gain COntrol |

| IP_MPA | Multi Port Access |

| IP_HP_DDR2 | High Performance DDR2 |

| IP_DBY | Debayer |

| IP_CCM | Color Correction Matrix |

| IP_GC | Gamma Correction |

| IP_OV | Overlay |

| IP_MMoE | Protocol Memory Map over Ethernet |

| IP_Gigabit | Link Ethernet 10/100/1000 |

IP_SPort – Sensor Port

This IP Sensor Port allows to reconstruct the standard signals for both CMOS and CCD interface sensors. The IP_SPort for CCD generates the timing pulses for performing progressive scan for CCD image sensor.

Key features

- Selectable bitwidth for input pixel data, HDR ready

- Integrated gain stage with selectable fixed-point precision bits for each RGB color channel

- Integrated I2C or SPI interface

- Dynamic setup via Wishbone

- Sensor interface for CCD and CMOS

| Resource Utilization Example Lattice XP2™ 12-bit CMOS Port |

|||

|---|---|---|---|

| LUT | Register | DSP | Fmax(MHz) |

| 376 | 344 | 2 | >100 |

IP_Stat – Statistics

This IP core provides pixel sum and pixel numbers for each color channel. This information is used for example by the AWB algorithms.

Key features

- Selectable bitwidth for input pixel data, HDR ready

- Column and row counter

- Freely adjustable ROI

- Counters for number of pixels in ROI, saturated pixels, etc.

- Dynamic setup via Wishbone

IP AWB/AGC – Automatic White Balance Automatic Gain Control

This IP core is aimed at automatically adjusts both the gain and the white balance of the scene to a neutral setting regardless of the ambient light source.

Key features

- Feedback from statistics

- Online optimal gain computation for each frame

- Set computed gain value to sensor register and FGPA register via a master Whisbone interface

- Customizable algorithm

- Resource optimized sMico32 calculation engine

IP_DBY – Debayering

This IP core is aimed at reconstructing the full color information for each sensor pixel. Several interpolation algorithms have been developed. The IP core allows to obtain a full color image where for each pixel a full set of R, G, B values are provided by interpolation. This results in a high-quality image.

Key features

- Selectable bitwidth for input pixel data, HDR ready

- Selectable maximum picture column size

- 3×3 bilinear, 5×5 high-quality

- Dynamic setup via Wishbone

- Border extrapolation

| Resource Utilization Example Lattice XP2™ 8-bit, 2048 column, 3×3 bilinear |

|||

|---|---|---|---|

| LUT | Register | EBR | Fmax(MHz) |

| 232 | 147 | 3 | >100 |

IP_CCM – Color Correction Matrix

Often the images acquired from a sensor have wrong colors . This is due to the cross color effect. The IP core corrects colors applying a correction matrix to each pixel.

Key features

- Selectable bitwidth for each color channel data, HDR ready

- Selectable bitwidth for coefficients /selectable fixed-point bits

- Full color RGB in- and output

- Auto saturation detection

- Dynamic setup via Wishbone

- Each matrix coefficient is a fixed-point number

IP_GC – Gamma Correction

The gamma correction allows to modify the relationship between a pixel’s numerical value and its actual luminance from a linear to non-linear relation.

Key features

- Selectable bitwidth for each color channel data, HDR ready

- Selectable output datawidth

- Automatic interpolation between look up table entries

- Separate correction for each single color channel

- Dynamic Setup via Wishbone

- Gamma Compression or expansion possible to switch during processing

IP_OV – Overlay

This IP core add text or graphics to a video stream. This allows to implement On-Screen Display function.

Key features

- Adjustable overlay position

- Selectable number of different colors

- 32-Bit per color

- Dynamic setup via Wishbone